基板での電気信号の伝搬速度について解説します。

電気信号の伝搬速度は、基板設計において最も基本的なパラメータの一つである配線の長さを判断する物差しになります。

この記事では、光速の半分とはどのくらいなのか?どうやって設計判断の物差しにするのか?を解説します。

- 基板設計の良否を判断する方法が知りたい方

- 基板設計スキルをアップさせたい方

- 高周波信号の基板設計に挑戦される方

光速の約半分

基板での電気の伝搬速度(V)は、以下の式で計算されます。

V = C / √ε

※Cは真空中の光速、εは導体周囲の比誘電率

基板で使われるガラスエポキシ樹脂の比誘電率は4.7くらいで、その平方根は約2.17となります。よって、光速の半分くらいが基板での電気の伝搬速度となります。光速は約30万km/s なので、その半分の15万km/sくらいです。

光速の半分とはどの程度か

光速の約半分、15万km/sと言われてもなかなかピンと来ないかも知れません。すごく早いという事は分かるので、”伝搬速度(遅延時間)を考える必要なんか無い” という考え方もありがちです。多くの基板において、その考え方でそんなに問題無いというのも事実です。

しかし、信号の周波数が上がってくるとそうも言ってられません。

そこでまずは15万km/sという速度を、基板で取り扱うような物差しに変換して記述してみます。

- 1mmの伝搬遅延は約7ps

- 周波数1GHzの信号波長は約140mm

この表現になると、基板設計中の物差しとして直接的に役に立ちます。2つほど例を挙げてみます。

CLK同期信号の配線長差

「出来る限り等長に配線してください。」といったような曖昧な設計指示がアプリケーションノートや設計指示書に記述されていることは良くあります。そのような場合に具体的な設計ルールを設定する手順を説明します。

この例では、100MHzのCLK同期信号を考えてみます。

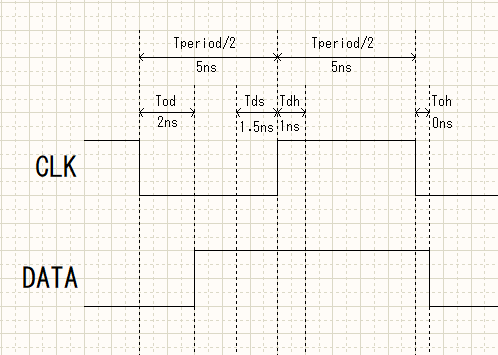

この信号の入力デバイスはCLKの立ち上がりでデータを取り込みます。このような場合、入力デバイスのデータシートには下記の2つのスペックが記述されています。

- Tds:CLK立上がりのxx秒前までにはDataの状態を確定していてください。

- Tdh:CLK立上がり後yy秒後まではDataの状態を保持してください。

今回は Tds = 1.5ns、Tdh = 1nsとします。

また、出力デバイスのデータシートに下記のようなスペックが記述されています。

- Tod:CLK立下がりからxx秒経過するまでにはDataの状態を確定します。

- Toh:CLK立下がりから少なくともyy秒はDataの状態を保持します。

今回は Tod = 2ns、Toh = 0ns とします。ここまでの内容を下図にまとめます。

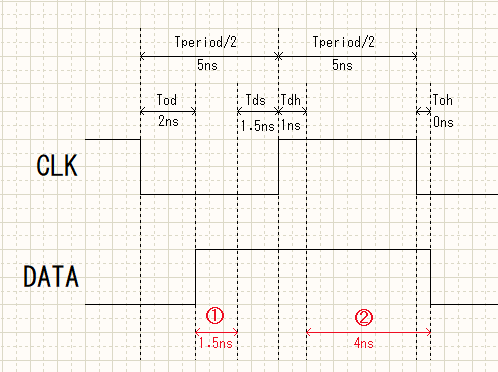

この図から、基板に許されるCLKとDATAの配線長差を読み取ります。

- CLKよりもDATAが1.5ns以上遅くなると、Tdsを満たせない可能性あり

- CLKよりもDATAが4ns以上早くなると、Tdhを満たせない可能性あり

これは下図の赤字のところになります。

この2点に ”1mmの伝搬遅延は約7ps” を加えて配線ルールにすると以下になります。

-214mm < CLK – DATA < 571mm

このルールを見てどう感じるでしょうか?以外と緩いんだなと感じたのではないでしょうか。現実的に、基板上でns(ナノ秒)単位の配線長差が出てしまう事は想定する必要が無さそうです。

オシロスコープのプロービング

電気信号の伝搬速度がどの程度かという感覚は、オシロスコープで信号波形やタイミングを評価する場合に非常に重要です。これが無いと、配線上で信号波形は均一であるという誤った認識をしてしまい、プローブはどこに当てても良いと判断してしまいます。

電気信号の波形品質やタイミングについては、当然ですがデバイスの入力端子で定義されています。ですので、オシロのプローブはデバイスの入力端子に当てるべきです。

150mmで等長配線されたCLK同期信号で誤って、CLKは入力端子に、DATAは出力端子にプローブしたとします。 150mm * 7ps/mm = 1050ps のタイミングずれがある状態の波形を見ていることになりますので、前項のような100MHz以上の信号では判断を間違える可能性があります。

さらに、出力端子にプローブしたDATA波形には、150mmの配線を往復してきた反射波が合成された波形になっているので、波形品質の判断も出来ません。波形立上り/下りから2100ps程度のポイントに反射波によるグリッジが出ているような波形が測定されそうです。

プローブのGNDも入力側デバイスの端子の直近に当てるべきです。基板のGNDも均一な電位と考える事は出来ません。

まとめ

プリント基板での電気信号の伝搬速度は光速の約半分です。これは、以下のように書き換えると考えると基板設計での物差しとして扱いやすいです。

- 1mmの伝搬遅延は約7ps

- 周波数1GHzの信号波長は約140mm

このような感覚は、パターン配線長のルールを設定したりオシロで波形評価する際に必要なものです。その重要性は、周波数が高いほど、配線が長いほど、高くなります。

その他のカン・コツ紹介記事

これ以外にもハード設計のカン・コツを紹介した記事があります。こちらも参考にしてみてください。

KiCAD (Pcbnew)の便利な使い方。作業効率アップのコツ

コメント